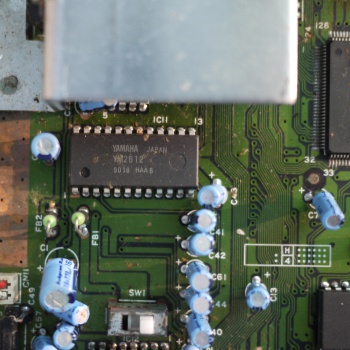

YM2612

The YM2612 (the smaller cousin of the YM2608) is the Sega Mega Drive's main sound chip. It is capable of outputting 6 channels of FM synthesis, allowing it to re-create almost any instrument with life-like precision by using built-in algorithms, feedback, and various other properties, which are specified by 'voices.'

Each channel is also capable of Stereo audio, allowing it to be output on either the left or right channel, or both.

In addition to FM synthesis, the YM2612 can replace the 6th FM channel with a DAC that can be used to re-produce accurate drums, snares, voice samples, and more. However, all timing has to be done in software, which usually limits sample quality, especially as the YM2612 requires 8-bit unsigned data. This, as well as the Z80's 'slow' bank reads often produced inferior sample quality, especially when software mixing was done by the driver to produce the illusion of having two DAC channels.

To access the YM2612, a program needs to write into a specific area of IO memory, which is often done by the Z80 when it runs the sound driver, or the M68k when it is running the sound driver.

If distortion of a channel's amplitude or frequency is required, the chip's LFO, or Low Frequency Oscillator can modulate each operator's amplitude and frequency to a specifiable extent.

Yamaha removed the better 14-bit accumulator-equipped sound mixer and replaced it with an easier and presumably cheaper to manufacture time-division sound multiplexer, which first truncates the 14-bit output to 9 bits, and then rapidly loops through outputting all channels. This truncation causes a glitch as the wave form approaches zero, also known as the 'ladder effect.' To solve this, external filtering circuitry is used which distorts the sound even further. Sega used an improved YM2612 in the Model 2 Mega Drive which does not have this issue, but problems with the sound filtering circuit cause a more distorted sound. Sega also used this chip in a number of its arcade game cabinets.

The YM2612 is programmed through a number of 8-bit registers, some being stitched together to form longer registers, such as with the timers. In this case, the most significant byte is written first. The timers have to be constantly polled by software to yield a result, mainly due to the fact that they do not cause an interrupt for either of the two processors due to a design deficiency. The constant polling of timers may cause some inaccuracies to occur.

Contents

Registers

As stated before, the chip is programmed through a number of registers. Due to the large number of registers available, writing to the YM2612 is divided into two parts. Part 1 has it's own data and address port, which is separate from Part 2. In general, Part 1 contains global chip control and registers for channels 1-3, whereas part 2 contains registers for channels 4-6.

Part 1

Below is a small map illustrating the arrangement of registers in Part 1:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

|---|---|---|---|---|---|---|---|---|

| $22 | LFO enable | LFO frequency | ||||||

| $24 | Timer A MSB | |||||||

| $25 | Timer A LSB | |||||||

| $26 | Timer B | |||||||

| $27 | Ch3 mode | Reset B | Reset A | Enable B | Enable A | Load B | Load A | |

| $28 | Operator | Channel | ||||||

| $29 | ||||||||

| $2A | DAC | |||||||

| $2B | DAC enable | |||||||

| $30+ | DT1 | MUL | ||||||

| $40+ | TL | |||||||

| $50+ | RS | AR | ||||||

| $60+ | AM | D1R | ||||||

| $70+ | D2R | |||||||

| $80+ | D1L | RR | ||||||

| $90+ | SSG-EG | |||||||

| $A0+ | Frequency LSB | |||||||

| $A4+ | Block | Frequency MSB | ||||||

| $A8+ | Ch3 supplementary frequency | |||||||

| $AC+ | Ch3 supplementary block | Ch3 supplementary frequency | ||||||

| $B0+ | Feedback | Algorithm | ||||||

| $B4+ | L | R | AMS | FMS | ||||

These registers are programmed through 4000h-4001h on the Z80 side, or A04000h-A04001h from the M68k side. Note that the data bus to the YM2612 is only 8 bits.

Part 2

Part 2's memory map is mostly the same as the one above - except the channels 1-3 in Part 1 are channels 4-6 in Part 2. The registers are however, differently from the first set, programmed through $4002-$4003 on the Z80 side, or $A04002-$A04003 from the M68k side.

$22 — LFO

The LFO can be used to distort each operator's amplitude and frequency to a certain degree at a pre-set frequency.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| LFO Enable | LFO Frequency | ||||||

- LFO Enable: Enables the LFO if set.

- LFO Frequency: Specifies the frequency that the LFO oscillates at.

- 0: 3.98 Hz

- 1: 5.56 Hz

- 2: 6.02 Hz

- 3: 6.37 Hz

- 4: 6.88 Hz

- 5: 9.63 Hz

- 6: 48.1 Hz

- 7: 72.2 Hz

In order for the LFO to affect a channel's sound, it must not only be globally enabled, but also enabled for each channel, and each operator using the appropriate registers.

$24 and $25 — Timer A

| $24 — MSB | |||||||

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Timer A MSB | |||||||

| $25 — LSB | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Timer A LSB | |||||||

Both registers are combined to hold the 10-bit value for Timer A. For the timer to function correctly, the MSBs must be written first, followed by the LSBs. To calculate the duration between the timer expiring, the following formula can be used:

t = 18 × (1024 - Timer A) µs

$26 — Timer B

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| Timer B | |||||||

To calculate the duration between the timer expiring, the following formula can be used:

t = 288 × (256 - Timer B) µs

$27 — Timer Control, Channel 3 Mode

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| Ch3 Mode | Reset B | Reset A | Enable B | Enable A | Load B | Load A | |

- Ch3 Mode; When set to

01each of Channel 3's operators will use a separate frequency, instead of using offsets of a single integral frequency. - Load: When set, the corresponding timer (A or B) is started and begins counting.

- Enable: Causes the corresponding timer to set the read register's overflow flag when set. When clear, the timer will never set this bit.

- Reset: Resets the read flag when written as set.

$28 — Key on/off

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| Operator | Channel | ||||||

| 4 | 3 | 2 | 1 | ||||

This register triggers the key on and off events for a channel. In most cases, all four operators will be set to receive a key on and key off event at the same time, but the ability to give each individual operator a key on/off event can be useful when used in conjunction with the special Channel 3 mode.

The channel values are as follows:

- Ch1:

000 - Ch2:

001 - Ch3:

010 - Ch4:

100 - Ch5:

101 - Ch6:

110

$2A and $2B — DAC

The YM2612 is capable of outputting 8-bit DAC, which can be used in place of the 6th FM channel. Many games use them for drums, snares, and voice samples. The YM2612 does not provide any buffering of timing of samples, so this has to be done in software, in almost all cases by using the Z80 for this task to avoid locking up the 68k, and the main game logic.

| $2A — DAC value | |||||||

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DAC Value | |||||||

| $2B - DAC Enable | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DAC Enable | |||||||

Unsigned 8-bit DAC data is written to register $2A, and will be output instead of the sixth FM channel when the DAC Enable bit in register $2B is set.

Undocumented Features

Register $2C

This undocumented register was found and researched by Oerg866 in April of 2012.

When Bit 5 of YM Register $2C is set to 1, panning gets affected by the L/R part of the L/R/AMS/FMS reg of these channels:

- $B4 in Bank 1 of the YM2612 for Channel FM1

- $B5 in Bank 1 of the YM2612 for Channel FM2

- $B6 in Bank 1 of the YM2612 for Channel FM3

- $B4 in Bank 2 of the YM2612 for Channel FM4

- $B6 in Bank 2 of the YM2612 for Channel FM6

One bit on either side drags panning of the PCM channel in said direction. They can be mixed, for example, to produce 'smooth' panning. (i.e. have some L and R bits enabled, but more L than R, will still have panning have priority on L)

Conclusion

- FM Waveform does not matter. The FM channel can be empty for all it cares.

- FM Total level does not matter (!)

- FM Key on does not matter (all key on bits can be set to 0 and it will still work)

- The only thing that actually affects PCM panning is how many FM channels have either the L or R bit set to 1

More information about this undocumented register can be found here.